학부생의 시선으로 작성한 내용입니다. 잘못된 내용이나 누락된 내용이 있을 수 있습니다. 잘못된 내용은 수정해 나가겠습니다. 누락된 내용은 제 이해 범위가 넓어질 때 차차 추가할 예정입니다.

목차:

II-1. 아날로그 vs 디지털 회로 설계

II-2. 스펙 분석과 결정

II-3. 추상 수준과 EDA

II-4. Standard Cell Library

II-5. 디지털 회로 설계 절차

II. 설계 지식

II-1. 아날로그 vs 디지털 회로 설계

MPW 제작에 사용하는 공정은 ETRI에서 제공하는 0.5㎛ Analog CMOS 2Poly 3Metal 공정이다. 공정명에 아날로그가 쓰여있는 것을 통해서 해당 공정이 디지털 회로 설계를 위한 것은 아님을 알 수 있다. 추가적으로 2 Ploy()라는 것은 두 개의 폴리 층(Poly Layer)이 제공된다는 뜻이다. 모스펫(MOSFET, Metal Oxide Semiconductor Field Effect Transistor)에 기본적으로 사용되는 Ploy Layer 외에도 추가적인 Ploy Layer가 한 층 더 제공된다는 뜻이다. 이 추가적인 Poly Layer는 축전기(Capacitor) 설계를 위한 것으로 이를 통해서도 해당 공정이 아날로그 공정임을 알 수 있다. 이번 MPW 제작에 있어서 아날로그 공정을 사용하면서 설계는 디지털 회로 설계를 하고자 한다. 자세한 내용을 제쳐 두고 도대체 아날로그와 디지털 회로 설계는 무엇이 다를까? MPW 제작에 참여하면서 생각한 아날로그와 디지털 회로 설계의 차이에 대한 내용을 정리했다.

|

|

| IDEC KAIST 강의실 뒤에 진열된 웨이퍼의 정보. 좌측은 1 Poly라는 정보에서 아날로그 공정은 아니라는 것을 알 수 있다. 반면 우측의 공정은 RF라는 표기 외에도 2 Poly를 통해서 아날로그 지원 공정임을 알 수 있다. 원래라면 지나칠 내용인데 눈에 걸리게된 것이 기쁘다. | |

아날로그 회로는 정해진 범위에서 무한한 개수의 값을 사용한다. 즉, 정해진 범위의 모든 데이터가 의미를 가진다. 예를 들어 어떤 입력에 대하여 아날로그 회로를 거쳐 나온 출력이 있다면 출력 신호의 모든 값은 의미를 가진다. 따라서 생성되는 출력 신호가 입력 데이터를 왜곡하지 않는 개형을 그리는 것이 중요하다. 회로의 저항(R), 유도계수(L), 전기용량(C)은 개형에 큰 영향을 미친다. 그러므로 아날로그 회로 설계의 목표 중 하나는 회로에서 만들어지는 모든 R, L, C 값을 고려하여 의도하지 않은 왜곡을 최소화하는 것임을 알 수 있다.

디지털 회로는 정해진 범위에서 유한한 개수의 값을 사용한다. 디지털 회로는 0과 1의 값을 가지는 디지털 스위치로 회로를 설계한다. 디지털 스위치 n개를 묶어서 n비트(Bit)를 구성하고 이를 통해 유한한 개수의 데이터를 표현한다. 예를 들어 8bit 데이터는 총 256개의 유한한 데이터를 표현할 수 있다. 디지털 회로는 아날로그 회로와 다르게 출력 신호의 개형보단 각 비트의 출력 신호가 얼마나 빠르게 0과 1을 오갈 수 있는지가 중요하다. 이런 특징으로 인해 풀업(pull-up)과 풀다운 (pull-down) 성능이 뛰어난 구조인 CMOS(Complementary Metal Oxide Semiconductor)를 사용한다. 회로의 R과 C는 전기 신호 전달에 지연(RC delay)을 만든다. 즉, R과 C는 0과 1 사이의 전환 속도에 영향을 미친다. 디지털 회로 설계의 목표 중 하나는 이러한 RC delay를 최소화하여 설계물의 성능을 원하는 수준으로 구현시키는 것임을 알 수 있다.

II-2. 스펙 분석과 결정

설계의 첫 단계는 스펙을 분석하고 결정하는 것이다. 스펙 분석은 설계물에 무엇이 필요한지 분석하는 것이다. 설계하는 칩이 목표로 하는 소비전력·성능·면적(PPA, Power Performance Area)을 분석한다. 칩이 사용될 시스템에 어떤 주변장치(Prepheral)가 있는지 분석하여 필요한 입출력 인터페이스(I/O interface)를 확인한다. 또한, 칩에서 사용할 알고리즘들을 분석하여 전용 하드웨어로 구현할 것과 소프트웨어로 구현할 것을 분류한다.

스펙 결정은 분석 내용을 토대로 실제 사용할 적절한 자원을 결정하는 것이다. 분석한 PPA에 적합한 공정을 결정한다. Prepheral을 분석한 내용을 바탕으로 I/O interface의 구체적인 스펙을 결정한다. 알고리즘 분석에서 전용 하드웨어를 사용한 경우 소프트 매크로(Soft macro)와 하드 매크로(Hard macro) 두 개의 선택지가 있다. 전자의 경우 하드웨어기술언어(HDL, Hardware Description Language)로 기술된 코드의 형태이다. 이를 소프트웨어 도구를 활용해 하드웨어로 구현하여 사용한다. 설계 목적에 적합하도록 수정 가능하다는 장점이 있다. 후자의 경우 이미 하드웨어로 완성된 형태이다. 알고리즘에 따라 면적에서 이득인 경우가 있고 완성된 형태이기에 바로 사용 가능하다는 장점이 있다. 두 선택지에서 설계 목표에 적합한 방식을 선택한다. 소프트웨어로 알고리즘을 구현하기로 했다면, 주어진 환경에서 구동 가능한 방식으로 소프트웨어를 설계한다.

이처럼 스펙을 정확히 분석하고 결정하기 위해서는 하드웨어와 소프트웨어 역량이 모두 요구됨을 알 수 있다. 이번 프로젝트에서는 공정이 ETRI의 0.5㎛ Analog CMOS 2P3M으로 고정되어 있었다. 또한, 설계한 칩은 어떤 시스템에 적용시키기 위한 것이 아니라 직접 제작한 Std-Cell Library의 실리콘 검증과 툴 체인(Tool Chain) 정립을 위한 테스트 칩에 가까웠다. 따라서 PPA에 대한 압박과 스펙 분석 및 결정에 대한 논의 비중이 크지 않았다. 하지만 이번 테스트 검증 이후에는 스펙에 대한 논의도 이루어질 것이기 때문에 상기한 역량을 갖춰야 할 것이다.

II-3. 추상 수준과 EDA

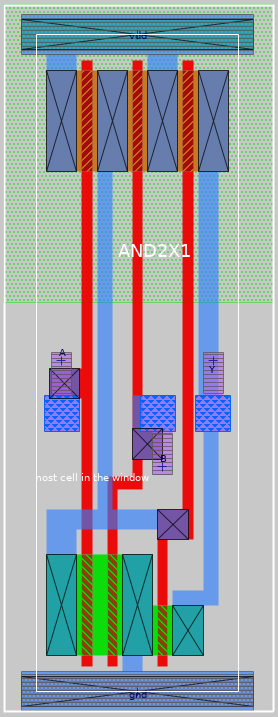

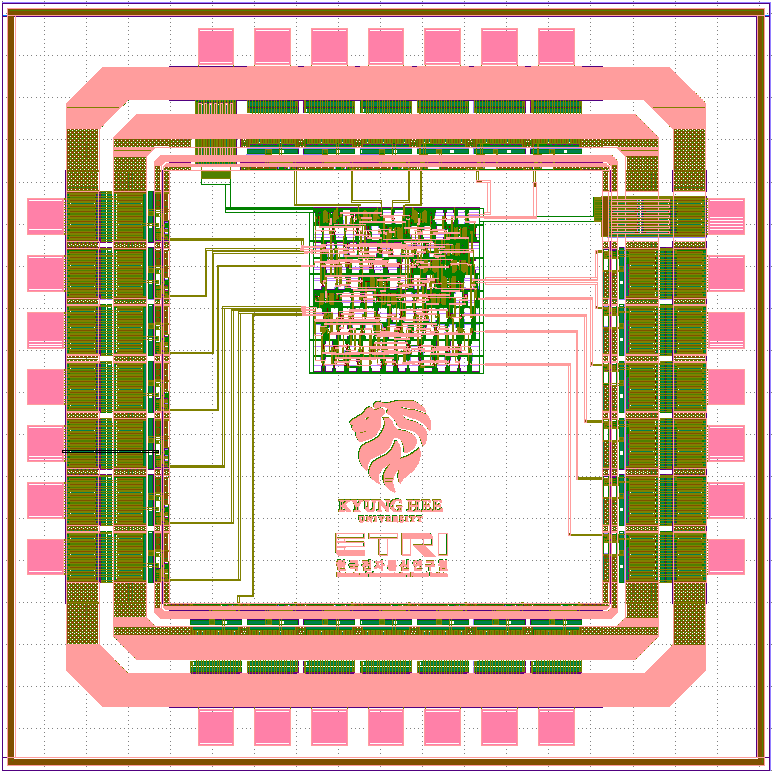

위의 사진은 실제 반도체 칩으로 제조 가능한 형태인 레이아웃(Layout)이다. Layout만을 가지고 이 회로가 어떤 행위(behavioral)를 하는지 알 수 있을까? 알아내기 위해선 Layout에서 논리게이트(Logic Gate) 간의 연결 구조(Structure)를 추출(Extraction)해야 한다. 그리고 이 연결 구조를 분석(Analysis)하여 회로의 행위를 알아낼 수 있다. 위의 칩은 두 개의 4bit 데이터를 더해서 5bit 크기로 출력하는 단순한 회로의 Layout이다. 이런 단순한 회로조차도 Layout을 통해서 회로의 행위를 알아낸다는 것은 매우 번거로운 일이다. 32bit 시스템, 64bit 시스템 등의 표기에서 알 수 있듯이 오늘날의 칩은 매우 복잡한 시스템을 가진다. 즉, 오늘날의 설계물들에 있어 Layout에서 칩의 행위를 얻어내는 것은 번거로운 일을 넘어 불가능에 가깝다. 이를 역으로 생각하면 오늘날에는 원하고자 하는 디자인을 물리 도메인(Physical Domain)에 해당하는 Layout부터 설계하는 것 역시 불가능하다는 것을 의미한다. 앞서 설명한 것처럼 시스템이 복잡해지면서 Layout은 더욱 복잡하고 구체적인 형태를 띠기 때문이다.

이미지 출처 : https://www.apple.com/kr/newsroom/2020/11/apple-unleashes-m1/

그러므로 반도체 설계를 하기 위해서는 이해가 쉬운 추상적인 형태부터 시작해야 함을 예상할 수 있다. 추상적이란 것은 무엇인지 예시를 통해 설명하겠다. '더한다'라는 개념은 추상적이다. '더한다'의 추상성은 그 개념이 사용되는 범위로부터 알 수 있는데 숫자와 숫자를 더하는 것, 두 색을 더하는 것, 심지어 행복을 더한다는 표현도 존재한다. 이중 숫자와 숫자를 더하는 개념조차 아직 추상적이다. 더해질 두 숫자가 정수인지, 실수인지, 서로 다른지 등 무수한 경우에 대하여 '숫자를 더한다'는 말로 표현할 수 있기 때문이다. 앞서 소개한 Layout으로 구현된 회로의 행위는 '두 4bit 데이터를 더한다'이다. '숫자를 더한다'는 개념과 비교하면 추상성이 낮다. 하지만 Layout의 입장에선 이 행위 자체는 여전히 추상적인 개념이다. 왜냐하면 '두 4bit 데이터를 더한다'라는 행위를 구현할 Layout의 형태는 매우 다양하게 존재하기 때문이다. 예시의 Layout은 직사각형으로 구현되었지만 같은 행위를 하는 정사각형꼴의 Layout도 구현가능하다. 즉, 실제로 생산에 사용된 Layout은 의도한 행위를 구현할 수 있는 수많은 Layout 중 하나의 구체적인 사례이다. Layout은 반도체 설계에 있어서 가장 낮은 추상성을 가지는 생산 가능한 물리적 형태로도 정의할 수 있다. 앞의 예시로 반도체 설계 과정을 정리하면 아래와 같다.

1. '더한다'라는 추상적인 개념에서 시작한다.

2. 추상성을 낮추어 '두 4bit 데이터를 더한다'라는 구체적인 행위를 결정한다.

3. 이 행위를 구현할 수 있는 다양한 물리적 형태들 중 하나를 실제 칩으로써 제조한다.

이처럼 오늘날의 칩 설계는 인간이 이해하기 쉬운 추상 수준에서 시작하여 추상성을 점진적으로 낮추는 과정으로 이루어진다.

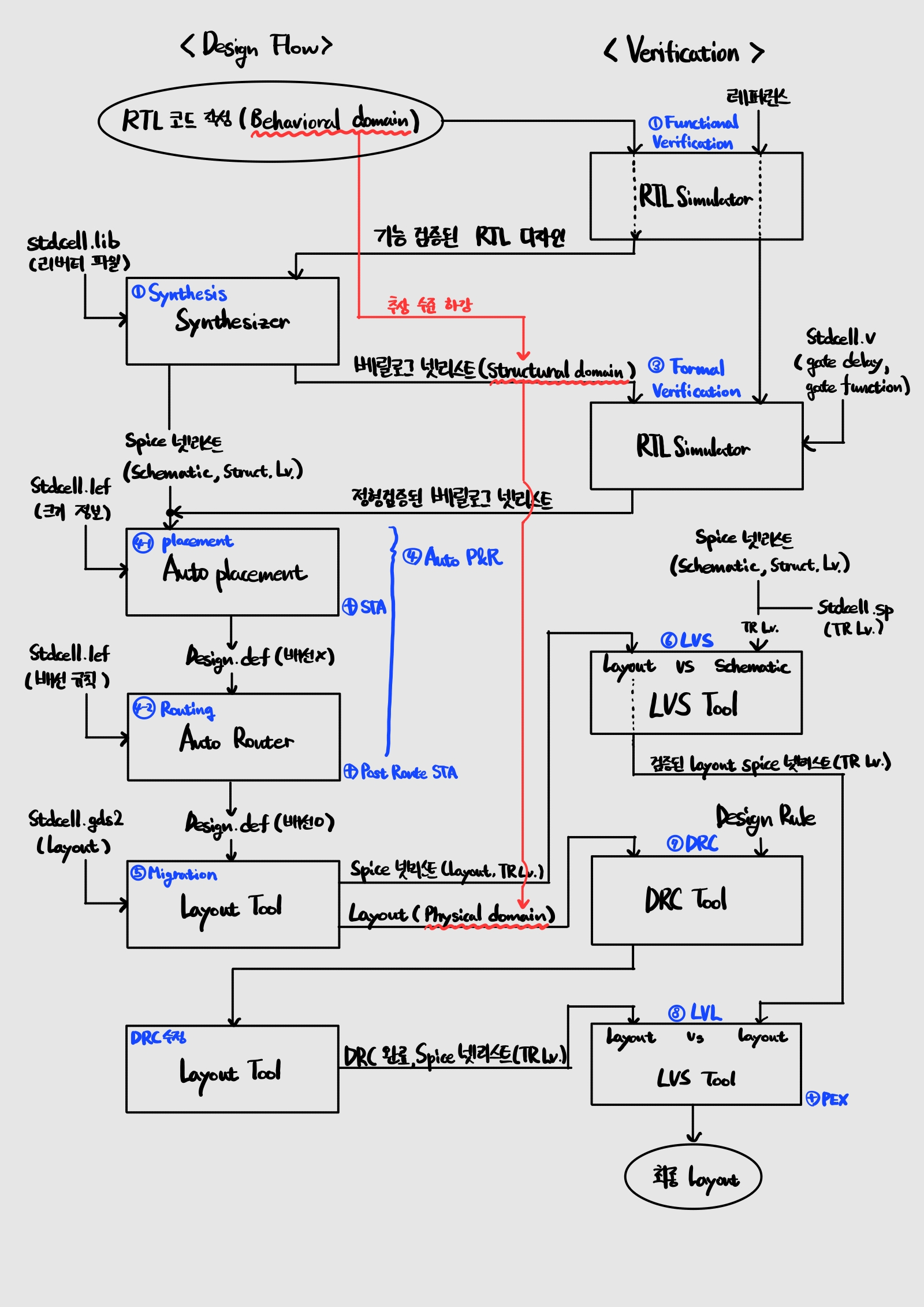

추상성을 낮추는 단계를 쪼개어 점진적으로 수행함에도 불구하고 시스템이 복잡할수록 이 또한 사람이 하기 쉽지 않다. 따라서 컴퓨터 소프트웨어의 도움을 받아 추상성을 낮추는 방법이 발전하였다. 추상성을 낮추는 과정 자체가 매우 복잡하기 때문에 이를 수행하는 소프트웨어의 잠재적인 오류 발생을 고려하지 않을 수 없다. 따라서 추상성을 낮춘 결과물의 유효성을 검증할 소프트웨어 역시 발전하였다. 반도체 설계와 검증을 목적으로 사용되는 이런 소프트웨어들을 전자설계자동화(EDA, Electronic Design Automation) 도구라 부른다. Y-diagram은 Daniel Gajski와 Robert Kuhn이 집적회로설계의 추상화 수준을 정립한 그림이다. 아래는 Y-diagram에서 사용하는 용어를 정리한 이미지이다. 칩 설계가 추상성을 낮추는 과정임을 이해했으므로 이미지의 Y모양으로 구분된 세 가지 도메인(Domain) 사이에 적절한 EDA 도구가 필요하다는 것을 파악할 수 있다. Behavioral Domain에서 Physical Domain 방향으로는 구체화(Refinement)라는 용어를 그 반대 방향은 추상화(Abstraction)라는 용어를 사용한 것 역시 이해할 수 있을 것이다. 아래의 다른 용어들도 우리가 베릴로그(Verilog)와 같은 HDL을 배우는 수업에서 자주 보던 용어들이기에 익숙할 것이다.

II-4. Standard Cell Library

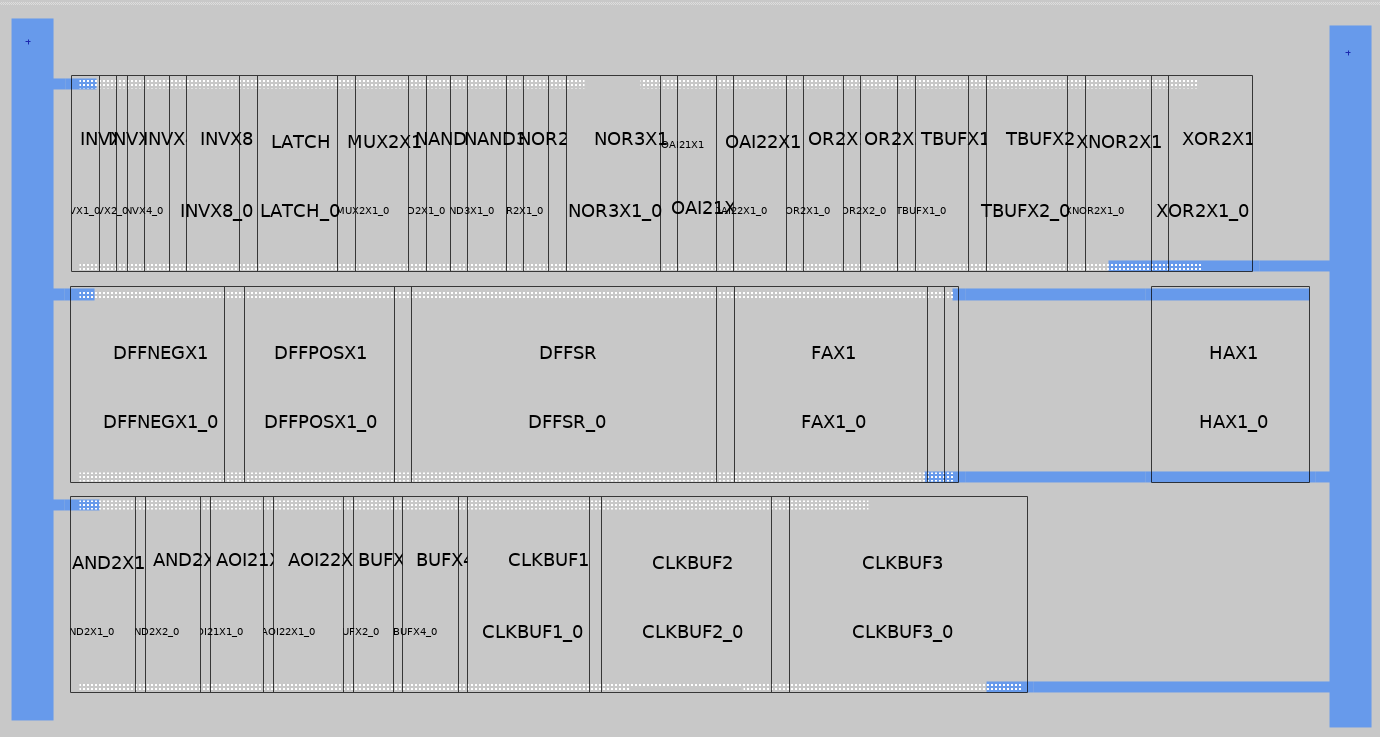

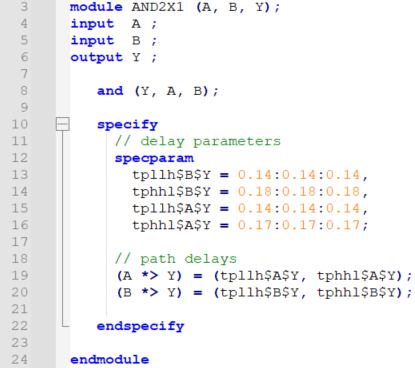

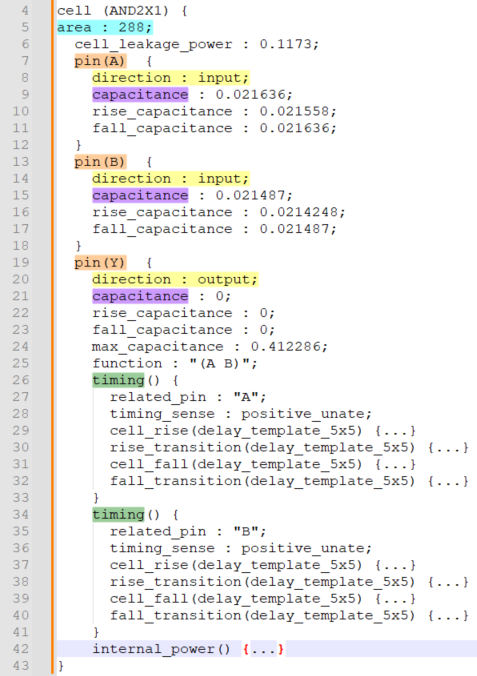

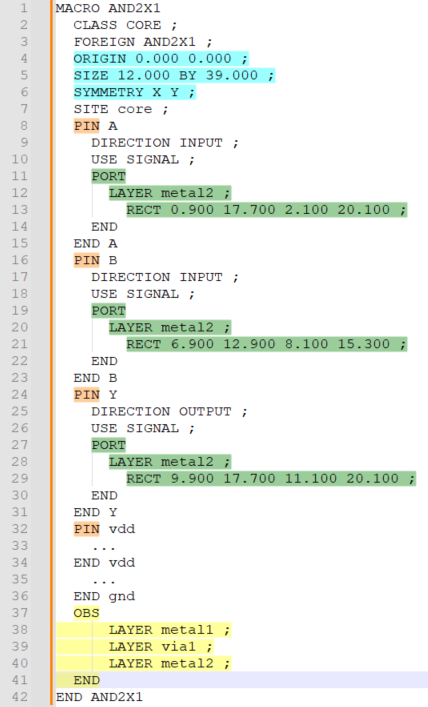

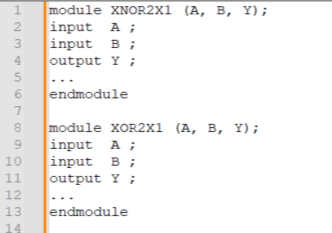

Std-Cell은 위의 사진처럼 (N)AND, (N)OR, NOT, X(N)OR와 같이 조합 회로를 위한 다양한 논리 게이트(Logic Gate)부터 플립-플롭(Flip-Flop), 레치(Latch)와 같은 순차 회로의 저장 요소들을 포함한다. 또한, 멀티플렉서(Mux, Multiplexer)나 가산기(Adder)와 같은 범용적인 조합회로도 Std-Cell에 포함된다. Std-Cell의 각 Gate들은 해당 공정에서 검증이 완료되어 설계의 가장 작은 단위(Cell)로써 활용 가능한 것들이다. Std-Cell 방식의 디지털 설계는 Std-Cell Library를 기반으로 정보전달수준(RTL, Register Transfer Level) 코드를 EDA 도구를 통해 Layout의 형태로 만드는 방식이다. Std-Cell의 Layout에서 눈에 띄는 특징은 Std-Cell의 높이가 모두 같다는 것이다. 이는 배치의 자동화를 위한 것이다. 설계 과정에서 Std-Cell들을 퍼즐처럼 배치하고 연결하는 과정이 존재한다. 동일한 높이를 가짐으로써 수평으로 전원 공급 라인을 그리고 이 라인에 Std-Cell들을 정렬시켜 배치 자동화를 보다 간편하게 구현할 수 있다. Std-Cell을 사용하여 layout을 만들기 위해서는 설계의 각 과정에서 필요한 Std-Cell의 정보가 다르다. 따라서 EDA 도구가 요구하는 파일 형식 역시 상이하다. 이러한 요구를 충족시키기 위해서 Std-Cell의 정보는 여러 파일 형식으로 관리된다. 이런 파일들의 집합이 Standard Cell Library이다. 아래 표와 이미지는 Std-Cell Library에서 관리되는 중요한 파일들에 대한 내용이다. 표와 이미지를 대조하여 확인하면 이해가 쉬울 것이다.

| 파일 형식 | 정보 |

| RTL 파일(stdcell.v) | 정형검증(Formal Verification) 및 자동 배치배선(Auto P&R, Auto Placement and Routing)에 사용하는 파일 형식이다. 합성(Synthesis)의 결과 중 하나인 Verilog 넷리스트(Netlist)는 구조적수준(Structural Level)에서 기술된 코드로 게이트 간의 연결관계가 기술되어있다. 이때 게이트들은 Std-Cell의 인스턴스(instance)이다. instance의 원본 모듈이 stdcell.v 파일에 작성되어있다. 주요 정보로는 Std-Cell의 논리식과 specparam형식으로 기술된 지연(Delay)정보이다. 합성 후 시뮬레이션에서 specparam의 Delay정보를 이용한다. |

| Liberty 파일(stdcell.lib) | Synthesis에 사용되는 파일 형식이다. Synopsys사에서 개발한 형식으로 Std-Cell의 다양한 물리적인 정보가 담겨있다. 입출력 방향과 그에 따른 타이밍 정보가 담겨있다. 이 값들은 배치 이후 정적타이밍시뮬레이션(STA,Static Timing Analysis)에도 사용된다 |

| Library Exchange Format 파일(stdcell.lef) | Auto P&R에 사용하는 파일 형식이다. Std-Cell들의 원점, 크기, 포트 위치 정보등의 기하학적 정보가 담겨있다. 또한 배선 과정에서 의도하지 않은 연결을 막기위한 Layer 금지구역(Obstruction)도 정의되어있다. Std-Cell 내부의 자세한 정보는 담겨있지 않다. |

| gds 파일(stdcell.gds) | Standard Cell의 layout이다. 배치 배선 정보만 담긴 def(Design Exchange Format) 파일과 함께 불러와 마이그레이션(migration) 과정에서 완전한 형태의 layout을 얻는데 사용된다. |

|

|

| stdcell.v의 AND2X1 module. 논리식과 Delay가 확인된다. | stdcell.lib의 AND2X1. Std-Cell의 물리적 정보가 담겨있다. |

|

|

| stdcell.lef의 AND2X1. Std-Cell의 기하학적 정보가 담겨있다. | stdcell.gds2의 AND2X1 Layout. |

II-5. 디지털 회로 설계 절차

1. RTL 코드 설계 & Functional Verification

스펙이 결정된 프로젝트에 대하여 RTL을 HDL로 기술한다. 작성된 RTL 코드를 검증한다. 테스트벤치(Testbench)를 작성하고 DUT(Design Under Test)에 테스트 벡터(Test vector)를 입력하여 원하는 결과가 나오는지 확인하여 검증할 수 있다. 또는 레퍼런스(Reference)를 두어서 Reference의 테스트 결과와 DUT의 결과가 일치하는지 확인할 수도 있다. 이 과정은 RTL 시뮬레이터를 통해 이루어진다. 논리적으로 원하는 기능을 하는지 검증하기 때문에 기능 검증(Functional Verification)이라고 부른다.

RTL 시뮬레이션에는 두 가지 문제가 있다. 문제점과 그 해결책에 대해 알아보겠다. 첫 번째 문제는 대규모 Testbench 작성이 어렵다는 것이다. HDL은 하드웨어를 기술하기 위한 목적의 언어이기 때문에 파일 단위로 입력과 출력을 받는 것이 어렵다. 이를 해결하기 위한 방법은 검증 특화 언어인 시스템베릴로그(Systemverilog)를 활용하는 것이다. Systemverilog는 객체지향프로그래밍(OOP, Object-oriented Programming)을 지원하며 파일 입출력 기능을 지원한다. 이를 이용해 UVM(Universal Verification Methodology) 환경을 만들어 검증하는 것으로 해결할 수 있다.

두 번째 문제는 RTL 시뮬레이션이 매우 오래 걸린다는 것이다. 매 클럭마다 모든 데이터의 비트별(Bitwise) 변화가 이벤트로 처리되기 때문이다. 32bit 시스템과 같이 수많은 데이터를 처리하는 시스템일수록 그 경우의 수는 급격히 늘어난다. 이를 해결하기 위한 방법은 시스템C(SystemC)로 트랜잭션 수준 모델링(TLM, Transaction-level modeling)을 하는 것이다. TLM에서는 특정 RTL 블록에 대응하는 소프트웨어를 RTL 블록의 Netlist로 치환하여 시뮬레이션할 수 있다. 이때 Bitwise가 아닌 데이터 변화를 이벤트로 시뮬레이션을 하므로 시뮬레이션 시간을 획기적으로 줄일 수 있다.

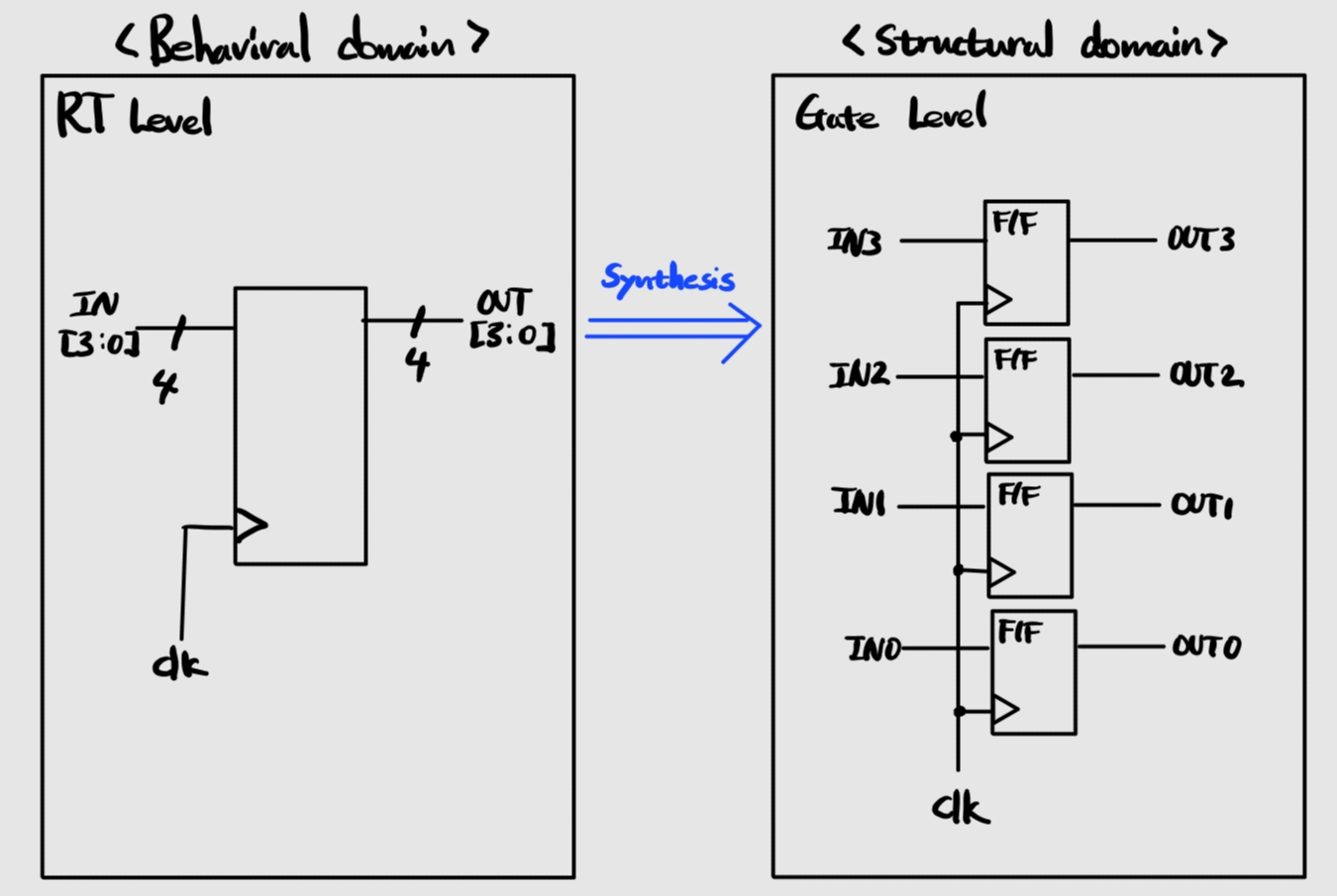

2. Synthesis & Formal Verification

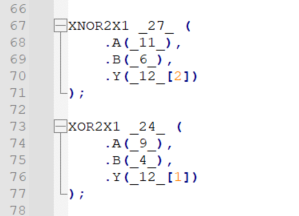

Functional verification이 완료된 RTL 코드를 합성기(Synthesizer)를 통해 Synthesis한다. Synthesizer는 Std-cell library의 lib파일을 참조한다. Synthesis의 결과로 게이트 사이의 연결 구조가 기술된 Netlist가 생성된다. Synthesizer는 설계물의 추상성을 Behavioral domain에서 Structural domain로 떨어뜨린다. 예시를 통해 설명하고자 4bit 병렬 레지스터(Parallel Register)의 합성 전후 모습을 가져왔다. 이미지를 보면 Behaviral domain에 해당하는 RT Level에서는 4bit 정보가 하나의 버스(Bus)로 표현되고 있고 출력 데이터가 클럭 엣지(Clock Edge)에서 최신화된다는 것을 알 수 있다. 이처럼 RTL에서는 행위를 쉽게 파악할 수 있다. 반면 합성 후의 모습은 Structural domain인 게이트 수준(Gate Level)에서 표현된다. Synthesis전과 비교하여 더 구체화되었기 때문에 회로를 파악하는데 시간이 필요하다. 4bit 전송을 위한 4개의 와이어(Wire)로 Bus가 구체화되었고 4bit 정보 저장을 위한 블록도 네 개의 Flip-Flop으로 구체화된 것을 확인할 수 있다.

앞서 II-3. EDA에서 언급했듯 추상화를 낮추는 것은 복잡한 작업이기에 EDA의 도움을 받는다고 했다. 또한, EDA의 잠재적인 오류 가능성을 염두하여 추상성을 낮춘 결과물의 유효성을 검증해야 한다고 했다. 따라서 Synthesis의 결과물인 Netlist가 원본 RTL 모델과 일치함을 보여 그 유효성을 검증한다. Funtional Verification 단계의 Reference를 이번에는 Synthesis 결과로 나온 Netlist와 비교한다. 이 과정을 통해 합성된 형태의 유효성을 검증하므로 정형 검증(Formal Verification)이라고 부른다. 이때 stdcell.v파일을 참조한다. stdcell.v파일을 참조하는 이유는 Gate Level Netlist의 경우 Std-Cell의 Instance들로 기술되어 있기 때문에 원본 Module의 정보가 필요하기 때문이다. Synthesis 되기 전에는 어떤 Std-Cell이 어떤 구조로 Synthesis 될지 알 수 없기 때문에 시간적 요소를 배제하고 시뮬레이션을 진행한다. 반면 Gate Level에서는 Std-Cell들이 드러나므로 Std-Cell Library의 Delay정보(stdcell.v에 specparam 형태로 기술되어 있음)를 활용한 타이밍 시뮬레이션(Timing Simulation)을 할 수 있다. 물리적인 시간에 대한 시뮬레이션 요소가 설계의 과정에서 처음으로 등장했다. Synthesis이후부터는 설계물이 Physical Domain에 가까워짐에 따라서 고려해야 할 시간적인 요소는 점점 다양해진다.

|

|

| Synthesizer가 만들어낸 Verilog Netlist의 일부. 원본은 모듈은 stdcell.v에 존재한다. |

stdcell.v파일에 기술된 Std-Cell의 모듈. 좌측의 Verilog Netlist에 사용된 Instance들의 원본이다. |

3. Place and Route, STA

게이트 사이의 연결 관계만을 나타낸 Netlist를 기반으로 자동 배치·배선(Auto P&R, Automatic Placement & Routing) 도구를 사용해 배치(Placement)와 배선(Routing)을 진행한다. Auto P&R 결과 파일 형식은 def로 Std-Cell의 위치, 포트 좌표와 배선 정보만이 담겨있다. Placement 단계에서는 Std-cell의 lef 파일에서 크기 및 대칭 정보를 읽어 Std-Cell이 들어갈 공간을 배치를 한다. 이때 생성되는 def 파일에는 아직 배선 정보가 들어있지 않다. Routing 단계에서는 lef파일의 입출력 포트 위치 정보와 par파일의 배선용 정보를 읽어 배선을 진행한다. 이후에 생성되는 def 파일에는 배선정보까지 완전히 담기게 된다.

STA는 lib파일의 RC값을 사용해 게이트 delay를 누산하여 목표로 하는 성능 이 합성 이후에도 나오는지 분석한다. 이때 아직 배선하기 전이므로 배선에 의한 RC delay는 고려되지 않는다. Post-Route STA는 배선을 완료한 layout에 대하여 Delay를 계산한다. 배선에 대한 RC 정보는 par파일에 기술되어 있다. STA결과에서 목표로 한 성능이 나오지 않는다면 배치와 배선을 최적화한다. 혹은 RTL 코드에서 플립플롭(Flip-Flop) 사이의 조합 회로에 의한 딜레이를 줄이는 방향으로 RTL 코드를 수정한다.

4. LVS & DRC, LVL

Auto P&R를 통해서 def 파일을 얻었고 이에 Std-Cell의 Layout을 포함시켜 완전한 Layout을 얻을 수 있다. 드디어 우리가 원하던 Physical Domain의 Layout을 얻었다. 추상성이 떨어졌으니 마찬가지로 유효성 검증을 한다. 검증은 총 세 가지 단계로 이루어진다.

첫 번째는 LVS(Layout versus Schematic)이다. Synthesis 과정에서 얻은 Formal Verification된 Netlist와 Auto P&R로 얻은 Layout의 Netlist를 비교한다. 전자는 회로도(Schematic)에서 얻은 Netlist이고 후자는 Layout에서 얻은 Netlist이기 때문에 둘의 비교를 Layout versus Schematic이라고 부른다. 이때 각 Netlist는 트랜지스터 수준(Transistor Level)의 Netlist이다. Reference로 사용되는 Schematic의 Netlist는 Gate Level이므로 이를 Transistor Level로 변환해주어야 한다. 변환을 위해서 Std-Cell Library에서 제공되는 Std-Cell의 Transistor Level Netlist를 참조한다. 이 과정에서 검증을 완료하면 EDA 도구를 사용해 Layout을 얻는 과정에 문제가 없었다는 것을 의미한다. 즉, EDA 도구를 활용하여 추상성을 떨어뜨리는 전 과정에 문제가 없었다는 것을 의미한다.

두 번째는 DRC(Design Rule Check)이다. Layout에는 반도체의 기하학적인 형상이 Layer로 표현되어 있다. 각 layer의 면적과 그들 간의 물리적인 거리는 공정에서 제공하는 공정키트(PDK, Process Design Kits)의 규칙을 지켜야 한다. DRC는 layout이 이러한 규칙을 위반하지 않았는지 검사하는 절차이다. DRC를 모두 통과했다면 공정을 진행할 때 내가 그린 Layout 그대로 큰 문제없이 생산된다고 생각할 수 있다.

세 번째는 LVL(Layout versus Layout)이다. DRC를 통해 Layout을 수정했기 때문에 해당 Layout의 Netlist는 더 이상 유효성이 보장되지 않는다. 따라서 DRC가 완료된 Netlist의 유효성을 검증해야 한다. DRC를 완료한 Layout Nelist와 LVS에서 검증된 유효한 Layout Nelist와 비교한다. 따라서 이를 Layout versus Layout이라고 부른다. LVL이라는 용어에서 알 수 있듯이 Reference와 검증대상 모두 Physical Domain에서 얻어진 Netlist이며 이제 다른 Domain의 정보는 더 이상 관여하지 않는다. 이런 점은 설계가 막바지에 왔음을 직감하도록 해준다. 이 과정까지 마무리되면 Design Rule에 위배되지 않아 정상적으로 생산되면서 의도한 행위가 물리적으로 구현된 Layout을 얻을 수 있다. 마침내 높은 추상 단계에서 시작하여 가장 추상성이 낮은 형태인 Layout을 얻은 것이다.

5. I/O Pad 작업 & GDS 추출

설계한 칩이 외부와 정보를 주고받을 수 있도록 I/O Pad 작업을 한다. I/O Pad는 외부의 전압으로부터 칩을 보호하기 위한 대한 보호 회로가 내장되어 있다. 칩의 I/O 종류와 수에 맞게 I/O Pad를 배치하고 칩과 배선한다. layout의 최종 형식은 GDS이다. GDS 파일은 기하학적 정보와 계층 구조(Hierarchy)를 가진 파일이다. 아래 이미지는 GDS 형식의 Layout 파일을 열어본 예시이다. GDS 파일을 Fab.에 넘겨주는 것으로 회로 설계가 마무리된다.

https://fun-teaching-goodkook.blogspot.com/ 내용을 참조하여 작성했습니다.

'MPW > 디지털 회로 설계' 카테고리의 다른 글

| [MPW/DCD]디지털 회로 설계(3)/맺음말 (0) | 2024.01.20 |

|---|---|

| [MPW/DCD]디지털 회로 설계(1)/개요 (0) | 2024.01.20 |